Port parall�le sur PC

On a vu l�utilisation de liaison s�rie sur un PC. On sait qu�elle s�accompagne de limitations de d�bit et de distance. => Pour am�liorer la distance, on utilise des modems.

=> Pour am�liorer le d�bit, la solution simple consiste � faire passer plusieurs bits en parall�le.

Toutefois cela pose des probl�mes de diaphonie ( interf�rences �lectromagn�tiques entre fils ), ce qui limite encore plus la distance. En outre il faut disposer d�un nombre de fils plus �lev�s d�o� un co�t plus �lev�.

On verra dans un premier temps le port parall�le des origines du PC ( SPP ) puis les diff�rentes �volutions permettant l�utilisation de modes de fonctionnement plus performants.

I) Historique

En 1981, IBM inclut un port parall�le sur le PC pour des transmissions plus rapides que les liaisons s�ries. Il est utilis� pour envoyer des donn�es � une imprimante, donc pour une transmission unidirectionnelle : Mode standard : SPP.

Ensuite on a connect� d�autres p�riph�riques demandant des liaisons entrantes en utilisant des astuces�������� ( utilisation de lignes de gestion entrantes pour lire des donn�es ) : Mode quartet ( Nibble mode ).

Puis on a d�velopp� des circuits �lectroniques permettant aussi les donn�es entrantes sur les lignes de donn�es : Mode octet ( Byte mode ).

Mais la transmission est limit�e en d�bit ( 150 ko/s sortant ), demande beaucoup de traitement logiciel ( pas de� DMA ), n�est pas d�finie par un standard �lectrique ce qui pose des probl�mes d�interop�rabilit�, est limit�e en distance par la puissance des drivers de ligne �lectroniques.

En 1991, un

nouveau standard ( IEEE1284 ) est d�velopp� incluant un lien bidirectionnel

haut d�bit ( plus du Mo/s ). Il demande de nouveaux circuits mais doit aussi

�tre compatible avec les anciens fonctionnements : Mode EPP.

S�il reste inf�rieur au d�bit du bus ISA (8Mo/s), il permet n�anmoins la r�ception de donn�es depuis des p�riph�riques tels que des lecteurs de CD-ROM ou disques durs. En plus du d�bit sup�rieur, les ports EPP sont bidirectionnels.

Encore plus r�cent, le port ECP (Extended Capacity Port) poss�de la particularit� d'�tre Plug and Play�������� ( branchez et utilisez). Il d�rive du port EPP et en poss�de les m�mes caract�ristiques. Sa particularit� est qu'il permet au p�riph�rique branch� sur celui-ci de s'identifier � la machine d�s le d�marrage. Ainsi l'imprimante peut s'autoconfigurer lors du lancement du syst�me d'exploitation (� condition que ce dernier et le BIOS soient eux aussi compatibles Plug and Play).

Chaque mode d�finit une m�thode de transfert des donn�es :

|

Sens de transfert |

Mode |

|

|

Unidirectionnel ( SPP ) |

PC vers p�riph�rique |

Mode standard |

|

P�riph�rique vers PC |

Mode quartet |

|

|

Mode octet |

||

|

Bidirectionnel ( semiduplex ) |

|

Mode EPP |

|

Mode ECP |

||

Les modes Standard et quartet peuvent �tre utilis�s sur tout circuit parall�le. On cr�e ainsi un lien bidirectionnel. Les autres modes demandent que le circuit �lectronique soit pr�vu pour ces fonctionnements.

Le choix du mode de

fonctionnement SPP, EPP ou ECP se fait dans le BIOS.

II) Description du port parall�le

�

Le port parall�le sur PC est fait de 17 signaux et 8 broches � la masse. Les signaux sont de 3 cat�gories :

![]()

+

Signaux de contr�le� ( 4 ) :

Contr�le de liaison ( Handshake = encha�nement de requ�tes/r�ponses pour le

�������� d�roulement de la transmission ).

+ Signaux d��tat ( 5 ) : Indication de l��tat des appareils, de cause de probl�me.

+

Signaux de donn�es ( 8 ) : Envoi de donn�es du PC vers le p�riph�rique seulement

� l�origine.

�

Dans la d�finition originale ( SPP : Standard Parallel Mode ), le port parall�le du PC servait � la connexion avec des imprimantes. C�est pourquoi on trouve des noms de broches li�s � l�impression :

|

Groupe |

SPP Signal |

In/Out

|

Signal Description

|

|

Contr�le |

/STROBE |

Out |

Actif bas. Le PC indique la pr�sence

certaine de donn�es valides sur la ligne ( elles le sont avant ). |

|

/AUTOFEED |

Out |

Actif bas. Indique � l�imprimante

d�ins�rer automatiquement un saut de ligne en plus du retour chariot � chaque

return. |

|

|

/SELECT IN |

Out |

Actif bas. Indique � l�imprimante

qu�elle est s�lectionn�e. |

|

|

/INIT |

Out |

Actif bas. Utilis� pour envoyer un

reset � l�imprimante. |

|

|

Etat |

/ACK |

In |

L'imprimante envoie une impulsion � 0

sur cette ligne pour indiquer � l'ordinateur qu'elle a bien re�u le caract�re

transmis et qu�il peut continuer la

transmission. |

|

BUSY |

In |

Cette ligne est

mise � 1 par l'imprimante lorsque son buffer de r�ception est plein (

contr�le de flux mat�riel ). Le PC doit attendre que cette ligne

revienne � 0 pour r�-�mettre. |

|

|

PE |

In |

L�imprimante indique qu�il n�y a plus

de papier ( Paper Error ) |

|

|

SELECT |

In |

Cette ligne indique

� l'ordinateur si l'imprimante est "on line" ou "off

line". |

|

|

/ERROR |

In |

L�imprimante indique une erreur au

PC. |

|

|

Donn�es |

DATA[8:1] |

Out |

8 lignes de donn�es- seulement en

sortie en SPP. |

Remarque: Ce tableau pr�sente les broches dans le cas de l��change de donn�es. Elles peuvent �tre utilis�es � autre chose dans le cas de proc�dures de gestion de la liaison ( phases de transition demandant l��change d�information de contr�le ). On peut aussi envisager l�utilisation du port parall�le pour une liaison avec un autre p�riph�rique qu�une imprimante.�

Remarque: /A ou nA indique � Compl�ment de A �. Ici cela indique des variables actives sur niveau bas.

��������������� Le lien entre le mat�riel et le logiciel se fait par des registres : Le port parall�le est install� � une adresse de base ADR ( 378h ou 278h habituellement ). Les registres du port parall�les sont au nombre de 3 :

|

Adresse |

Nom |

Read/Write |

Description |

|

ADR + 0 |

Registre de donn�es (Data

Register) |

R/W |

Data port ( lecture/�criture de donn�es ) |

|

ADR + 1 |

Registre d��tat (Status

Register) |

R |

Contient les bits d��tat ( Status bits ) |

|

ADR + 2 |

Registre de contr�le (Control Register) |

W |

Utilis� pour imposer les valeurs des bits de contr�le |

��������������� Le brochage sur une prise DB25 sur le PC est le suivant :

����������������� BROCHE�� NOM�������������� Sortie du

PC����� Entr� dans le PC

����������������� -------------------------------------------------------------------------

����������������� 1������� /STROBE���������� X���������������� X

����������������� 2������� D0��������������� X���������������� X si EPP (voir apr�s )

����������������� 3������� D1��������������� X���������������� X si EPP����

����������������� 4������� D2��������������� X���������������� X si EPP

����������������� 5������� D3��������������� X���������������� X si EPP

����������������� 6������� D4��������������� X���������������� X si EPP

����������������� 7������� D5��������������� X���������������� X si EPP

����������������� 8������� D6��������������� X���������������� X si EPP

����������������� 9������� D7��������������� X���������������� X si EPP

����������������� 10������ /ACK�������������������������������� X

����������������� 11������ BUSY�������������������������������� X

����������������� 12������ PE���������������������������������� X

����������������� 13������ SELECT������������������������������ X

����������������� 14������ /AUTOFEED����������������� X���������������� X

����������������� 15������ /ERROR������������������������������ X

����������������� 16������ /INIT������������ X���������������� X

����������������� 17������ /SELECT IN������� X���������������� X

����������������� 18-25��� MASSE������������ X���������������� X

��������������� Le d�tail du registre de donn�es en ADR est :

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

D7 =

MSB |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 =

LSB |

������������������������������ Il n�est accessible qu�en �criture dans les premiers modes SPP.

��������������� Le d�tail du registre d��tat en ADR+1 est :

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

BUSY |

/ACK |

PE |

SELECT |

/ERROR |

Non d�fini |

Non d�fini |

Non d�fini |

Il n�est accessible qu�en lecture.

��������������� Le d�tail du registre de contr�le en ADR+2 est :

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Non d�fini |

Non d�fini |

DIR |

IRQ

ENABLE |

SELECT IN |

/INIT |

AUTOFEED |

/STROBE |

������������������������������ Il est accessible en lecture et en �criture.

Le bit 4 autorise ou non une interruption lorsque ACK passe � 0 ( l�imprimante valide la

R�ception d�un caract�re ).

Le bit 5 ne sert que pour les modes bidirectionnels : Ce bit � 1 rend le port accessible en �criture.

III) Mode normaux : SPP ( standard parallel port )

��������������� � Mode standard ( Mode Centronics ou Compatibility mode )

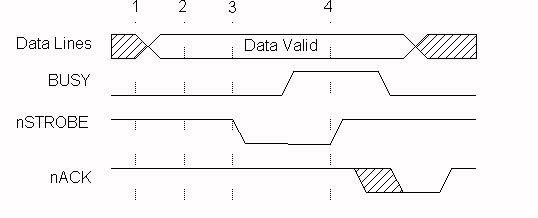

��������������� C�est le mode utilis� pour le fonctionnement normal du port SPP : Les donn�es sont plac�es sur les lignes de donn�es.

�

1. Ecrire les donn�es dans le registre de donn�es� ( => Elles sont sur les fils de sortie )

2. Lire le registre d��tat pour v�rifier que l�imprimante n�est pas occup�e ( BUSY )

3. Si elle ne l�est pas, �crire le registre de contr�le pour mettre� /STROBE = 0.

4. Ecrire le registre de contr�le pour changer /STROBE� et pouvoir passer � la donn�e suivante.

On

arrive � des d�bits de l�ordre de 150 ko/s. C�est suffisant pour les veilles

imprimantes mais pas pour les lecteurs CD amovibles ou les imprimantes lasers.

En outre c�est un mode unidirectionnel, du PC vers le p�riph�rique.�

‚ Mode Quartet ( Nibble mode )

��������������� Le mode Nibble est le moyen simple d�obtenir en SPP des donn�es du p�riph�rique vers le PC. Il est combin� avec le mode pr�c�dent pour obtenir une liaison bidirectionnelle ( voir norme IEEE1284 ).

��������������� On va utiliser comme entr�es de donn�es les entr�es de status. Un p�riph�rique enverra un octet de donn�es en envoyant 2 quartets ( nibbles ) � la suite.

Comme le /ACK est utilis� pour les interruptions, on utilise les 4 autres entr�es restantes ( BUSY, PE, SELECT, /ERROR ). Les bits sont donc �parpill�s dans le registre d��tat ce qui oblige � des traitements pour r�cup�rer un quartet puis l�octet

�

|

Signal SPP |

Nom en mode quartet |

In/Out |

Description � Utilisation

lors d�un transfert entrant en mode quartet |

|

/STROBE |

/STROBE |

Out |

Pas utilis� en transfert entrant. |

|

/AUTOFEED |

HostBusy |

Out |

Signal de handshake du PC en mode quartet. Mis bas pour indiquer que le PC est pr�t au mode quartet. Mis haut pour indiquer au p�riph�rique qu�un quartet a �t� re�u. |

|

/SELECTIN |

1284Active |

Out |

Mis � l��tat haut pour indiquer un transfert entrant ( 1284 ) |

|

/INIT |

/INIT |

Out |

Pas utilis� en transfert entrant. |

|

/ACK |

PtrClk |

In |

Au

niveau bas, indique une donn�e entrante valide, Mis � l��tat haut en r�ponse � HostBusy passant au niveau haut. |

|

BUSY |

PtrBusy |

In |

Utilis� pour le bit de donn� entrant 3, puis 7 |

|

PE |

AckDataReq |

In |

Utilis� pour le bit de donn� entrant 2, puis 6 |

|

SELECT |

Xflag |

In |

Utilis� pour le bit de donn� entrant 1, puis 5 |

|

/ERROR |

/DataAvail |

In |

Utilis� pour le bit de donn� entrant 0, puis 4 |

|

DATA[8:1] |

Non utilis�s |

|

En SPP les circuits �lectroniques n�acceptent pas le sens entrant. |

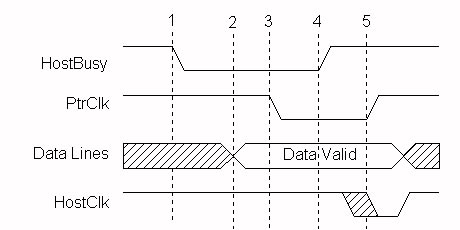

1. Le PC indique sa capacit� � recevoir un quartet en mettant HostBusy au niveau bas.

2. Le p�riph�rique r�pond en pla�ant le premier quartet sur les lignes d��tat utilis�es pour les donn�es.

3. Le p�riph�rique indique la validit� du quartet en passant PtrClk � bas.

4. Le PC met HostBusy � haut pour indiquer qu�il a re�u le quartet et qu�il n�est pas pr�t pour le suivant.

5. Le p�riph�rique met PtrClk haut pour acquitter cette information.

6. On recommence les �tapes 1 � 5 pour le second quartet.

Le mode quartet permet une liaison bidirectionnelle de donn�es malgr� un circuit �lectronique unidirectionnel pour ses lignes de donn�es.� Mais le d�bit est limit� � 50 ko/s.

ƒ Mode Octet ( Byte mode )

��������������� Des fabriquants ont install� un port parall�le bidirectionnel �lectroniquement. Mais la gestion reste la m�me qu�auparavant. On parle de "enhanced bi-directional" port � ne pas confondre avec Enhanced Parallel Port (EPP) qui va introduire des �l�ments de gestion plus performants.

��������������� Ici on a une �volution �lectronique ( entr�es de donn�es bidirectionnelles dont le sens est command� par le bit 5 DIR du registre de contr�le ) mais la gestion du transfert reste la m�me ( lire les signaux d��tat en attendant jusqu�� ce qu�ils prennent l��tat souhait�, �tablir les niveaux des signaux de contr�le selon la proc�dure ).

|

Signal

SPP |

Nom en mode Octet |

In/Out |

Description � Utilisation

lors d�un transfert entrant en mode octet |

|

/STROBE |

HostClk |

Out |

Signal d�acquittement. Mis bas pour indiquer que l�octet a �t� re�u. |

|

/AUTOFEED |

HostBusy |

Out |

Signal de Handshake. Mis bas pour indiquer que le PC est pr�t pour un octet. Mis haut pour indiquer que l�octet a �t� re�u. |

|

/SELECTIN |

1284Active |

Out |

Mis � l��tat haut pour indiquer un transfert entrant ( 1284 ). |

|

/INIT |

/INIT |

Out |

Pas utilis�, laiss� haut. |

|

/ACK |

PtrClk |

In |

Mis bas pour

indiquer des donn�es valides sur les lignes de donn�es, Mis haut en r�ponse � HostBusy passant au niveau haut. |

|

BUSY |

PtrBusy |

In |

Signal Busy du PC. |

|

PE |

AckDataReq |

In |

Suit /DataAvail |

|

SELECT |

Xflag |

In |

Drapeau d�extensibilit�. Pas utilis� en mode octet. |

|

/ERROR |

/DataAvail |

In |

Mis bas par le p�riph�rique pour indiquer qu�une donn�e entrante est disponible. |

|

DATA[8:1] |

DATA[8:1] |

Bi-Di |

Envoi des donn�es du p�riph�rique au PC. |

1. Le PC signal qu�il est pr�t � recevoir en mettant HostBusy bas

2. Le p�riph�rique r�pond en pla�ant les donn�es sur les lignes de donn�es

3. Le p�riph�rique indique que l�octet est valide en passant PtrClk � bas

4. Le PC met HostBusy haut pour indiquer qu�il a re�u et qu�il n�est pas encore pr�t pour un suivant

5. Le p�riph�rique� met

PtrClk haut pour acquitter cette information. Le PC applique une impulsion

pour��

��� acquitter � son tour.

6. On recommence les �tapes 1 � 5 pour le second octet.

��������������� Le mode octet de lire un octet sur les lignes de donn�es. On y arrive par des entr�es �lectroniques bidirectionnelles, le sens de transmission est choisi par un bit de direction dans le registre de contr�le : DIR.

��������������� On a donc en fait une liaison unidirectionnelle dont le sens est param�trable. On devra adapter par programmation logicielle les signaux de gestion au sens choisi => gestion lourde et p�nible.

=>D�bit encore limit� ou consommation de ressources du syst�me.

��������������� Les modes �tendus d�velopp�s en 1991 donnent des circuits �lectroniques am�lior�s par des machines d��tat ( circuits logiques s�quentiels ) qui g�n�rent automatiquement les signaux de contr�le.

��������������� => Le circuit devient aussi contr�leur de l��change parall�le.

IV) Modes �tendus

��������������� �

Mode EPP ( Enhanced Parallel Port )

��������������� Le mode EPP donne en plus du circuit �lectronique d��change parall�le un syst�me de contr�le de l��change selon le protocole EPP alors qu�avant on devait programmer ce syst�me de handshake. On l�a trouv� � partir du chipset Intel 386SL ( chip d�I/O 82360 ). On a en fait un contr�leur de communication parall�le.

Remarque : Sur les PC actuels on un contr�leur AIP ( Advanced Integrated Peripherical = Intel ) qui int�gre contr�leur de port s�rie, port parall�le, de disquette,�

��������������� Le protocole EPP fournit 4 types de cycles de transfert de donn�es :

������������������������������ - Ecriture de donn�es ( Data_Write cycle )

- Lecture de donn�es ( Data_Read cycle )��������������������

- Ecriture d�adresse ( Address_Write cycle )

- Lecture d�adresse ( Address_Read cycle )

��������������� Les cycles de transfert de donn�es sont ceux de SPP bidirectionnel pr�c�dent. On a en plus les cycles de transfert d�adresse. On passe en fait des adresses, commandes ou informations de contr�le. Ce sont en fait 2 cycles de transfert de donn�es qui s�encha�nent automatiquement.�

Signaux SPP |

Nom du signal EPP |

In/Out |

Description � Utilisation

lors d�un transfert EPP |

|

/STROBE |

/WRITE |

Out |

Actif bas, Indique

une op�ration d��criture. Il doit �tre haut pour un cycle de lecture. |

|

/AUTOFEED |

/DataStrobe |

Out |

Actif bas, il indique qu�une op�ration Data_Read ou Data_Write est en cours. |

|

/SELECTIN |

/ADDRStrobe |

Out |

Actif bas, il indique qu�une op�ration Address_Read ou Address_Write est en cours. |

|

/INIT |

/RESET |

Out |

Reset du p�riph�rique, Actif bas. |

|

/ACK |

/INTR |

In |

Interruption cr��e par p�riph�rique. Utilis� pour g�n�rer une interruption sur le PC. |

|

BUSY |

/WAIT |

In |

Signal de Handshake. Bas, il indique que l�on peut d�marrer un cycle ( appelle un strobe ). Haut, il indique que l�on peut terminer un cycle ( permet au strobe de conclure ). |

|

D[8:1] |

AD[8:1] |

Bi-Directionnel |

Lignes bidirectionnelles de donn�es, d�adresse |

|

PE |

D�fini par l�exploitant |

In |

Usage selon le p�riph�rique |

|

SELECT |

D�fini par l�exploitant |

In |

Usage selon le p�riph�rique |

|

/ERROR |

D�fini par l�exploitant |

In |

Usage selon le p�riph�rique |

La figure suivante est un exemple d��criture d�une donn�e : Data_Write cycle . Le signal /IOW de la CPU est montr� juste pour mettre en �vidence que tous les contr�les du port parall�le ( les autres signaux ) se font en un seul cycle d��criture CPU.

Cycle d��criture de donn�es EPP : Data_Write Cycle

1. Le programme demande une �criture ( I/O CYCLE ) � l�adresse du port parall�le ADR+4 (EPP Data Port)

2. La ligne /write de la liaison parall�le est activ�e et les donn�es plac�es en ligne.

3. Le /DataStrobe est activ�e pour signaler leur validit�, en cons�quence /WAIT est mis bas automatiquement par le p�riph�rique

4. Le port parall�le attend la remont�e de /WAIT comme acquittement par le p�riph�rique.

5. Le /DataStrobe est d�sactiv� ce qui est la fin du cycle EPP.

6. Le cycle ISA d�I/O est fini d�o� l��volution de /IOW

7. /WAIT est mis bas par le p�riph�rique pour indiquer qu�un nouveau cycle peut commencer.

La nouveaut� importante est dans le fait que le transfert complet d�une donn�e ( avec gestion de validit�, acquittement ) se d�roule sur un seul cycle d�entr�e/sortie ISA. Ainsi on arrive � 2Mo/s. On est proche du fonctionnement d�une carte interne ISA ( 6 Mo/s ). Avec les handshakes imbriqu�s, la vitesse sera fix�e par le terminal le moins rapide.

La

notion de Handshakes imbriqu�s signifie que chaque transition d�un signal de

contr�le est acquitt�e par un signal de l�autre c�t� de l�interface. Sur le

diagramme pr�c�dent, on voit que

/DataStrobe �volue parce que /WAIT est bas,

/WAIT remonte en r�ponse � la descente de /DataStrobe,

/DataStrobe remonte en r�ponse � la remont�e de /WAIT,

/WAIT descend en r�ponse � la remont�e de /DataStrobe.

Remarque : On trouve des composants EPP qui ne respectent pas

exactement la norme IEEE1284 d�finissant EPP���

( Au d�but du cycle, /DataStrobe ou /AddrStrobe prendra son �tat sans

s�occuper de /WAIT. Le p�riph�rique ne peut pas bloquer le d�but de cycle en

maintenant /WAIT. C�est la version EPP des premiers contr�leurs Intel 82360 ).

Exemple

d�un cycle Address_Read.

Registres intervenant pour le mode EPP

��������������� On retrouve les 3 registres de SPP auxquels on en ajoute 2 autres . Pour un port // install� � l�adresse ADR :

Nom |

Adresse |

Mode |

Read/Write |

Description |

|

Registre de donn�es SPP |

ADR |

SPP/EPP |

W |

Port de donn�es

standard SPP. Pas de gestion automatique ( autostrobing ). |

|

Registre d��tat

SPP |

ADR+1 |

SPP/EPP |

R |

Lecture des entr�es d��tat de l�interface. |

|

Registre de contr�le SPP |

ADR+2 |

SPP/EPP |

W |

Ecriture des sorties de contr�le. |

|

Registre

d�adresse EPP |

ADR+3 |

EPP |

R/W |

Lance un cycle d��criture ou de lecture d�adresse avec gestion automatique. |

|

Registre de donn�es EPP |

ADR+4 |

EPP |

R/W |

Lance un cycle d��criture ou de lecture de donn�es avec gestion automatique. |

|

Non d�fini |

ADR+5 � +7 |

EPP |

N/A |

Utilis� selon fabricants de p�riph�riques. Peut �tre utilis� pour entr�es/sorties 16 ou 32 bits. |

En g�n�rant une simple

instruction d��criture en ADR+4, le contr�leur EPP g�n�re automatiquement les

signaux de Handshake et de Strobe n�cessaires pour que le transfert suive le

cycle EPP Data_Write.

Des acc�s aux registres

SPP ( en ADR, ADR+1, ADR+2 ) am�nent un comportement identique au modes d�finis

auparavant.� Cela garantit la

compatibilit� avec les vieux syst�mes.

Un acc�s au registre

d�adresse EPP ( ADR+3 ) cr�era un cycle de lecture ou �criture

d� � adresse � selon /WRITE.

��������������� Le mode EPP en plus d�automatiser par le mat�riel la gestion de liaison ce qui permet des d�bits plus �lev�s, des logiciels moins lourds, permet aussi le m�lange facile de cycles de lecture et d��criture ainsi que le transfert de blocs par les cycles d�adresse.

‚ Mode ECP ( Extended

Capability Port )

��������������� Le port ECP propos� par HP et Microsoft permet en plus des performances de transmission du mode EPP de d�finir un protocole d��change d�informations de gestion du mat�riel.

��������������� Le protocole ECP autorise les cycles suivants dans les 2 sens :

������������������������������ - Cycle de donn�es

������������������������������ - Cycle de commandes������ -> Comptage RLE ( Compression Run Lenght Encoding ).

����������������������������������������������������������������������������� -> Adressage de canal.

��������������� La

r�alisation est standardis�e, d�finie dans le document Microsoft "The IEEE 1284 Extended Capabilities Port

Protocol and ISA Interface Standard".

��������������� ECP introduit la possibilit� de

compression RLE avant transmission, d�utilisation de m�moires FIFO et

d�utilisation de transfert DMA ( Direct Memory Access ).

��������������� La compression en temps r�el

permet d�atteindre des taux de 64 pour les liaisons avec imprimante ou scanner

( image pr�sentant des parties de pixels similaires ).

��������������� L�adressage de canal permet

d�adresser plusieurs appareils logiques sur une seule liaison physique�������������� ( exemple d�un appareil faisant

fax/modem/imprimante ou scanner/imprimante ). On peut utiliser les diff�rentes

fonctions de l�appareil en m�me temps.

|

Signal SPP |

Nom

du signal ECP |

In/Out |

Description � Utilisation

lors d�un transfert ECP |

|

/STROBE |

HostClk |

Out |

Utilis� avec PeriphAck pour transf�rer information sortante concernant donn�e ou adresse. |

|

/AUTOFEED |

HostAck |

Out |

Fourni Command/Data status en sortie. Utilis� avec PeriphClk pour transf�rer des donn�es entrantes. |

|

/SELECTIN |

1284Active |

Out |

Mis haut quand le PC est en mode de transfert 1284. |

|

/INIT |

/ReverseRequest |

Out |

Mis bas pour mettre le canal en direction inverse. |

|

/ACK |

PeriphClk |

In |

Utilis� avec HostAck pour transf�rer des donn�es entrantes. |

|

BUSY |

PeriphAck |

In |

Utilis�

avec HostClk pour transf�rer information sortante concernant donn�e ou adresse. Fourni Command/Data status en entr�e. |

|

PE |

/AckReverse |

In |

Mis bas pour acquitter /ReverseRequest. |

|

SELECT |

Xflag |

In |

Drapeau d�extensibilit� ( Extensibility flag ). |

|

/ERROR |

/PeriphRequest |

In |

Mis bas par le p�riph�rique pour indiquer qu�une donn�e entrante est disponible. |

|

Data[8:1] |

Data[8:1] |

Bi-Directionnel |

Echange des donn�es. |

Quand HostAck est haut, cela indique un cycle de donn�es.

Quand HostAck est descendu, cela indique un cycle de

commandes.

Les donn�es sont alors soit un comptage RLE ( si bit8=0 ),

soit une adresse de canal ( Si bit8=1 ).

Cycles de donn�es sortantes et de commandes en mode ECP

Transitions dans un transfert sortant:

1. Le PC place les donn�es sur les lignes de donn�es, indique qu�il lance un cycle de donn�es avec HostAck � 1.

2. Le PC descend HostClk pour indiquer que les donn�es en ligne sont valides.

3. Le p�riph�rique acquitte en montant PeriphAck.

4. Le PC monte HostClk. Le front montant d�clenche la lecture par le p�riph�rique.

5. Le p�riph�rique descend PeriphAck pour indiquer qu�il est pr�t � un octet suivant.

6. Le cycle recommence sauf que cette fois c�est un cycle de commandes car HostAck est bas.

Cycles de donn�es et de commandes entrants en mode ECP

1. Le PC demande un canal entrant en descendant /ReverseRequest.

2. Le p�riph�rique donne son accord en descendant /AckReverse.

3. Le p�riph�rique place les donn�es sur les lignes de donn�es et indique un cycle de donn�es en montant PeriphAck.

4. Le p�riph�rique descend PeriphClk pour indiquer que les donn�es en ligne sont valides.

5. Le PC acquitte en montant HostAck.

6. Le p�riph�rique monte PeriphClk. Sur le front montant, le PC lit la donn�es.

7. Le PC descend HostAck pour indiquer qu�il est pr�t � un octet suivant.

8. Le cycle se r�p�te sauf que c�est un cycle de commandes car PeriphAck est bas.

Contrairement � EPP, les signaux I/O READ ou WRITE ne sont

pas repr�sent�s sur les sch�mas pr�c�dents car ECP utilise des FIFO qui

permettent de d�coupler les transfert internes au PC ( bus ISA, DMA,� ) avec

les transferts sur la liaison parall�le.

On constate aussi que contrairement � EPP o� l�on peut

mixer entr�es et sorties sans dialogue ou ajout de donn�es, en mode ECP, un

changement de direction doit �tre n�goci�. Le PC demande un transfert sur canal

entrant en descendant /ReverseRequest et attend ensuite l�acquittement du

p�riph�rique par mise � 0 de /AckReverse. C�est une complication du logiciel de

gestion surtout si on interrompt une liaison DMA. ECP n�est donc pas fait pour

les alternances de direction sur des petits transferts mais pour des gros.

On

d�finit diff�rents modes de fonctionnement � l�int�rieur du mode ECP :

|

Mode |

Description |

|

000 |

SPP mode |

|

001 |

Mode Bidirectionnel (Byte mode) |

|

011 |

Mode ECP |

|

110 |

Test mode |

|

111 |

Configuration mode |

|

Autres |

Selon

l�utilisation de FIFO |

Le registre ECR ( Extended Control Register ) permet de d�finir le mode de fonctionnement. Il permet aussi de savoir si le mat�riel est apte au mode ECP.

|

Bit

7 |

Bit

6 |

Bit

5 |

Bit

4 |

Bit

3 |

Bit

2 |

Bit 1 |

Bit 0 |

|

Mode ( selon tableau

pr�c�dent ) |

Interruption ECP |

Autorisation mode DMA |

Bit de service ECP |

FIFO pleine |

FIFO Vide |

||

�

Description des registres en mode ECP d�un port install� en ADR :

|

Offset |

Nom |

Read/Write |

Mode de fonctionnement |

Fonction |

|

ADR |

Donn�es |

R/W |

000-001 |

Registre de donn�es |

|

ADR |

EcpAfifo |

R/W |

011 |

FIFO d�adresses ECP |

|

ADR+1 |

dsr |

R/W |

Tous |

Registre d��tat |

|

ADR+2 |

Dcr |

R/W |

Tous |

Registre de contr�le |

|

ADR+400h |

CFifo |

R/W |

010 |

FIFO des donn�es du port parall�le |

|

ADR+400h |

EcpDfifo |

R/W |

011 |

FIFO des donn�es ECP |

|

ADR+400h |

Tfifo |

R/W |

110 |

FIFO de test |

|

ADR+400h |

CnfgA |

R |

111 |

Registre de configuration A |

|

ADR+401h |

CnfgB |

R/W |

111 |

Registre de configuration B |

|

ADR+402h |

Ecr |

R/W |

Tous |

Registre ECR ( Extended Control Register ) |

��������������� Le mode ECP est d�fini par le BIOS.

Puis un mode de fonctionnement est d�fini dans le registre ECR ( bits 7 � 5 ).

Remarque : Les registres de configuration A et B ne sont accessibles qu�en mode Configuration. Ils permettent d�affiner la configuration de la liaison ( DMA, RLE, IRQ, gestion des erreurs ).

V) Aspects �lectriques d�une liaison bidirectionnelle

Comme pour n�importe quelle liaison on doit assurer un minimum de perturbations afin d�atteindre le meilleur d�bit ( pas trop de r�sistances internes, d�effets capacitifs qui font un filtrage RC ).

L�autre probl�me est la gestion du sens de transmission. En liaison s�rie, on dispose d�un fil RX de r�ception, d�un fil TX d��mission. En revanche la liaison parall�le bidirectionnelle consiste � g�rer le sens sur une m�me fil.

��������������� Le port parall�le de PC originel n�avait pas de sp�cification ( ni driver, terminaison de ligne, capacit� ) permettant de garantir la compatibilit�.

��������������� Les derni�res normes IEEE1284 concernant le port parall�le de PC d�finissent 2 niveaux d�interface.

������������������������������ - Niveau I : Pour les liaisons bas d�bit mais n�cessitant les 2 sens de transmission.

������������������������������ - Niveau II : Pour les hauts d�bits, les longs c�bles.

��������������� Nous verrons ici seulement le

niveau II, le plus exigeant. Les caract�ristiques sont :

��������������� Pour l��metteur :

������������������������������ - En circuit

ouvert, le niveau haut ne doit pas d�passer +5,5V, le niveau bas �0,5V.

- VOH

> 2,4V pour I = 14mA, VOL < 0,4V pour I = 14mA,

������������������������������ -

La r�sistance de sortie apr�s connecteur Ro = 50 +/- 5 W

������������������������������ -

Le slew rate doit �tre entre 0,05 et 0,40 V/ns.

��������������� Pour le r�cepteur :

������������������������������ - Le r�cepteur

doit accepter des pics de tension entre �2V et +7V sans dommage.

- Les

niveaux de d�cisions doivent �tre tels que�

VIH < 2V et VIL > 0,8V.

������������������������������ -

Le r�cepteur doit avoir en entr�e une hyst�r�sis de plus de 0,2V, de moins de

1,2V.

- Le

courant de fuite au niveau haut ne d�passe pas 20�A � 2V.

������������������������������ -

Le courant d�entr�e au niveau bas ne d�passe pas 20�A � 0,8V.

������������������������������ -

La capacit� �quivalente d�entr�e doit �tre inf�rieure � 50pF.

��������������� La figure suivante pr�sente la terminaison recommand�e. Ro repr�sente l�imp�dance de sortie apr�s connecteur. On suppose qu�il y a adaptation d�imp�dance avec le c�ble ( Rs sert � arriver � ce r�sultat ).

Si l�on int�gre la liaison bidirectionnelle, on arrive � la liaison

suivante :

VI) N�gociation du type de liaison parall�le

��������������� Comme un p�riph�rique n�est pas sens� supporter tous les modes de fonctionnement du port parall�le, il va falloir d�tecter les modes possibles et se mettre d�accord sur l�utilisation d�un d�eux.

��������������� Pour cela on r�alise une n�gociation initi�e par l�h�te : S�quence d��v�nements auxquels un ancien p�riph�rique ne r�pondra pas alors qu�un p�riph�rique supportant les modes r�cents r�pondra..

��������������� Durant la n�gociation, l�h�te place une requ�te ( code = extensibility data byte ) sur les fils de donn�e et lance la s�quence :

Diff�rentes phases lors de la n�gociation IEEE1284:

1. L�h�te place la requ�te ( extensibility data byte ) sur les fils de donn�es.

2. Il met /SelectIn � l��tat haut /AutoFeed bas pour indiquer une s�quence de n�gociation.

3. Un p�riph�rique 1284 r�pondra en mettant /Ack bas, /Error, PE et Select hauts.

Un p�riph�rique ancien ne r�pondra pas.

4. L�h�te met /Strobe � l��tat bas. Cela sert � indiquer que l�Extensibility byte peut �tre lu.

5. L�h�te met /Strobe et /AutoFeed � l��tat haut pour dire au p�riph�rique qu�il l�a reconnu comme capable des modes 1284.

6. Le p�riph�rique r�pond en mettant PE bas, /Error bas si il peut �mettre des donn�es ( canal entrant l�h�te ) et� Select � l��tat haut si le mode demand� par l�h�te est r�alisable ou Select bas sinon.

7. Le p�riph�rique met /Ack � l��tat haut pour indiquer la fin de la n�gociation et sa capacit� � communiquer dans le mode choisi.

Remarque: XFlag ( Select ) sert au p�riph�rique � indiquer que le

mode demand� est possible. Il sera toujours � 1

��� si c�est le cas

( Etape 6 de la figure pr�c�dente ) sauf pour un canal de retour en mode

quartet ( Nibble ).

��� En effet tout

appareil doit le supporter de toute fa�on, c�est le mode de base du canal de

retour..

Le code �mis ( extensibility byte ) permet de demander un mode de transfert mais aussi de demander au p�riph�rique de s�identifier.

��������������� N�gociation et identification d�un p�riph�rique permettent d�avoir un syst�me performant permettant un rattachement facile des p�riph�riques par le port parall�le.

Remarque : Il est d�j� pr�vu de nouvelles �volutions par des liaisons am�lior�es ( Extensibilty link ).

Valeurs possibles l�octet d�extensibilit� ( extensibility byte ) :

|

Description |

Valeurs valides |

|

|

Demande une liaison

� am�lior�e � (

Extensibility Link ) |

1000 0000 |

|

|

Demande de mode EPP |

0100 0000 |

|

|

Demande de mode ECP

avec RLE |

0011 0000 |

|

|

Demande de mode ECP

sans RLE |

0001 0000 |

|

|

R�serv� |

0000 1000 |

|

|

Demande

d�identification ( Device ID ) |

Avec retour des donn�es par le mode: |

|

|

Quartet ( Nibble ) |

0000 0100 |

|

|

Octet ( Byte ) |

0000 0101 |

|

|

ECP sans RLE |

0001 0100 |

|

|

ECP avec RLE |

0011 0100 |

|

|

R�serv� |

0000 0010 |

|

|

Mode Octet |

0000 0001 |

|

|

Mode quartet |

0000 0000 |

|

VI) C�ble parall�le direct

Un cas particulier de liaison parall�le est la connexion directe comme le NULL MODEM en liaison s�rie. Le but est de supprimer toute la proc�dure de contr�le.

Voir td